# Project for Energy Storage on a Chip for MEMS

J. Hubálek<sup>1</sup>, M. Schneider<sup>1,2</sup>, R. Hrdý<sup>1</sup>, J. Prášek<sup>1</sup>, U. Schmid<sup>1,2</sup>

<sup>1</sup>Centre SIX, Department of Microelectronics, FEEC, Brno University of Technology, Technická 3058/10, 616 00 Brno, Czech Republic

<sup>2</sup> Institute of Sensor and Actuator Systems, TU Wien, Gusshausstrasse 27-29, Vienna, Austria

e-mail: hubalek@feec.vutbr.cz

# Abstract

A new project with a budget of 262 thousands Euro was motivated by the lack of micromachined energy storage solutions that can be integrated with a MEMS harvester on a chip with a specific circuitry. These key components of the system are highly needed for autonomous microsystems and have to be integrated to enable an energy-autonomous, but efficient operation The targeted energy storage device needs to be charged very slowly from harvesters with output energies in the  $\mu$ Ws range. As a consequence, tailored materials and technologies for the realization of thin-film capacitors compatible with CMOS technology are of utmost importance. Target capacitance value about one hundred  $\mu$ F/cm<sup>2</sup>, low loss factor and low leakage currents are the expected properties of these devices.

## Introduction

Energy storage for MEMS harvesters integrated on a chip with a specific circuitry is a key feature for the successful operation of autonomous micro systems. Integration of the energy storage on a chip conditions the when targeting CMOS compatibility. The idea of energy storage on a chip is based on utilizing the back side of the silicon die. By exploiting the full chip area will help to create capacitors of enough high capacitance values. One electrode of the capacitor will be connected to the chip electronics, the second one with ground via e.g. package as it is shown in Fig. 1. The proposed capacitor is suitable for integrated MEMS harvesters based on e.g. piezoelectric, thermoelectric and electrostatic approach. Due to their low output currents, ultra-low loss factors as well as leakage current levels need to be assured. Current technologies offer low capacitance (MOS capacitor) or high leakage currents or an encapsulated electrolyte e.g. for electrochemical supercapacitors, thus making the latter approach technologically most challenging. A rough estimation of the generated energy from low power harvesters is about 100 nW. When the supply voltage will be 5 V, then the charge will be about 72  $\mu$ C/hour. A capacitance of 15  $\mu$ F will be necessary to store this amount of charge. Due to the direct consumption, efficiency of conversion below 5 V and self-discharging, a capacitance between 100-200  $\mu$ F is needed to store the generated energy on a daily basis.

*Fig. 1: Schematic block diagram of an integrated circuit and an energy capacitor in one package.*

Technology state of the art

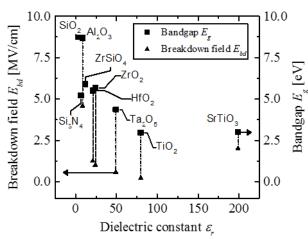

The standard MOS capacitor was developed for integrated circuits. It is made of a semiconductor formed by a heavily doped n+ poly-silicon layer as one electrode. Silicon oxide (SiO<sub>2</sub>) as a gate dielectric has seen tremendous improvements in CMOS technology over the last few decades yielding high quality insulation with ever decreasing film thickness. At the beginning of the MOS technology the thickness of dielectric was about 1000 Å and capacitance tens of nF/cm<sup>2</sup> enabling to create capacitors on a chip of about tens pF. Current technologies use less than 20 nm of dielectric thickness and capacitors of hundreds of pF. The MOS capacitor is a MIS structure which makes its capacitance depending also on the applied voltage. The fundamental thickness limitation of SiO<sub>2</sub> is given by increasing tunnelling leakage currents, prompting a search for alternative dielectric response at typical frequencies used in CMOS devices is mainly dominated by ionic and electronic polarization, potential candidates can be found in material systems where heavy metals with a large number of electrons (e.g. transition metals like Ta, Nb, Hf, Zr) form ionic bonds to oxygen. Figure 2 shows common high-k dielectrics. It is apparent, that there is a compromising relationship between the static dielectric constant, the bandgap E<sub>g</sub> and the electrical breakdown field strength E<sub>bd</sub>.

Given these requirements, promising dielectrics for on chip energy storage are Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub>, combining high dielectric constants and low leakage currents. Ta<sub>2</sub>O<sub>5</sub> (as well as SrTiO<sub>3</sub>) undergoes deleterious reactions with an underlying silicon substrate at high temperatures of ~700°C [4, 5], thus a low temperature oxidation step for porous tantalum thin films will be necessary. Amorphous tantalum pentoxide prepared by anodization presents good dielectric properties (dielectric constant of 25–27) complemented by high thermal, chemical and long term stability [6, 7]. ZrO<sub>2</sub> is isomorphous to HfO<sub>2</sub>, but it is slightly unstable and can form ZrSi<sub>2</sub> with silicon [8]. HfO<sub>2</sub> exhibits a high thermal stability and is therefore a very promising candidate for this application, but it exhibits a significantly lower dielectric constant compared to Ta<sub>2</sub>O<sub>5</sub>.

Fig. 2: Dielectric constant, bandgap and breakdown field strength of selected dielectrics [1].

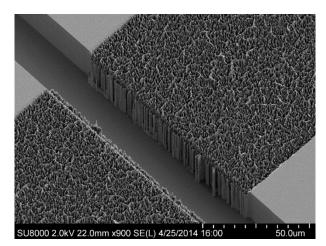

IPDiA has developed 3D silicon capacitor based on SiO<sub>2</sub> dielectric using deep structures. The technology capability is determined by density of 250 nF/mm<sup>2</sup> and properties such as reliability and stability up to 200°C, low temperature coefficient, low ESR, low ESL, and leakage current down to 100 pA. Deep Reactive Ion Etching (DRIE) is standard technique using so called Bosch process to obtain deep structures (pores or columns) followed by Atomic layer deposition of dielectric film. Lower electrode is highly doped silicon film, top electrode is purely metallic or as bilayer with poly-crystalline silicon stack. 2D and 3D structures prepared by photo-electrochemical etching were also demonstrated. This wet technique uses electrochemical etching in hydrofluoric acid (HF), where pores grow in perpendicular to the surface direction and pore walls become passivated against dissolution. The process is supported by photo-generation of minority carries from the backside of the wafer using UV lamp [9]. Another technique uses randomly formed mask for Si etching to obtain high aspect ratio structure [10]. Porous structure has not uniform shape after HF etching (Fig. 3).

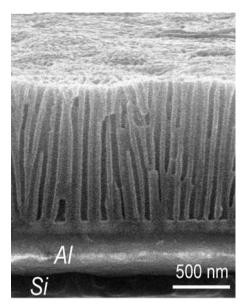

Other techniques do not use silicon etching. A very promising technique for the realization of deep porous structure is unconventional approach using sputtering of Ta film forming spontaneously directly to columns. Advantage of the structure is a simple oxidation procedure of Ta to form a dielectric film on the structure [11]. Mozalev

demonstrated two different approaches: i) formation of porous alumina covered with an anodic film of Ta and ii) anodization of bilayer Al/Ta to grow nanopillars of  $Ta_2O_5$ . The first approach was published in [12] as an on-chip

Fig. 3: Porous electrode structures of an electrolyte based supercapacitor in the device layer on a SOI wafer.

Fig. 4: SEM cross-sectional micrograph of Al/Ta sputtered film anodized at 51 V [10].

high-frequency integral capacitor. The aluminium was consumed by anodization to generate a  $\sim 1 \ \mu m$  thin porous mask. Tantalum oxide was formed on sputtered Ta film in the porous alumina (Fig. 4). The leakage currents resulted in the range of  $(3-20) \cdot 10^{-12} \ A \ mm^{-2}$ . Obtained capacitance values of 6.4 nF cm<sup>-2</sup> are still low for energy storage applications, but other parameters such as low leakage current levels are very promising.

## The project aim

Ultra-low-power systems or even zero-power systems are developed for implantable, mobile and wearable applications. Typically, these applications require the full integration of energy autonomous systems which besides the electronics also comprise components as key elements generating energy for their power supply. Therefore, integrated circuits and energy harvesters are integrated together with the help of microtechnologies. Another key component still missing to date is energy storage offering the capability to be integrated on a chip. Such solution is of utmost importance for an energy autonomous operation of the system because micromachined harvesters generate low immediate power which has to be stored for later use or the energy is generated for partial time only and has to be accumulated for operational periods where e.g. data are collected by sensors, conditioned by electronics on a chip level and sent wirelessly to a data base for final evaluation. Integration of miniaturized capacitors with a capacity of uF to mF within the mentioned systems is highly desired. This project aims to close this gap by developing adequate CMOS or MEMS compatible technologies and methodologies for on-chip integration of capacitors based on high-k dielectrics. We expect to created such devices using developed technologies with target capacitance value of about  $100 \,\mu\text{F/cm}^2$ , loss factor in the level of  $10^{-3}$  and leakage currents below  $10^{-11} \,\text{A/mm}^2$ .

### Acknowledgment

The presented research has been funded by Czech Science Foundation under grant no. 17-27340S. For the experimental part of the research, we used laboratories of the SIX Research Center supported by the National Sustainability Project LO1401 INWITE.

### References

- [1] J.H. Choi, Y. Mao, J.P. Chang, Development of hafnium based high-k materials—A review, Materials Science and Engineering: R: Reports 72 (2011) 97

- [2] J.-P. Locquet, C. Marchiori, M. Sousa, J. Fompeyrine, J.W. Seo, High-k dielectrics for the gate stack, Journal of Applied Physics 100 (2006) 051610.

- [3] S. Hall, O. Buiu, I.Z. Mitrovic, Y. Lu, W.M. Davey, Review and perspective of high-k dielectrics on silicon, Journal of Telecommunications and Information Technology 2 (2007) 33.

- [4] G.B. Alers, D.J. Werder, Y. Chabal, H.C. Lu, E.P. Gusev, E. Garfunkel, T. Gustafsson, R.S. Urdahl, Intermixing at the tantalum oxide/silicon interface in gate dielectric structures, Applied Physics Letters 73 (1998) 1517

- [5] K. Eisenbeiser, J.M. Finder, Z. Yu, J. Ramdani, J.A. Curless, J.A. Hallmark, R. Droopad, W.J. Ooms, L. Salem, S. Bradshaw, C.D. Overgaard, Field effect transistors with SrTiO3 gate dielectric on Si, Applied Physics Letters 76 (2000) 1324.

- [6] Chaneliere 1998] C. Chaneliere, J.L. Autran, R.A.B. Devine, B. Balland, Tantalum pentoxide (Ta2O5) thin films for advanced dielectric applications, Materials Science & Engineering R-Reports 22 (1998) 269.

- [7] D. Mills, L. Young, F.G.R. Zobel, Ionic conductivity dielectric constant and optical properties of anodic oxide films on 2 types of sputtered tantalum films, Journal of Applied Physics 37 (1966) 1821.

- [8] M. Copel, M. Gribelyuk, E. Gusev, Structure and stability of ultrathin zirconium oxide layers on Si(001), Applied Physics Letters 76 (2000) 436.

- [9] T. Trifonov, A. Rodriguez, L.F. Marsal, J. Pallares, R. Alcubilla, Two- and three-dimensional microstructures produced by electrochemical etching of silicon, Spanish Conference On Electron Devices, IEEE Proceedings 2005, p. 233-236.

- [10] A. Backes, U. Schmid, Impact of doping level on the metal assisted chemical etching of p-type silicon, Sensors and Actuators, B: Chemical 193 (2014) 883.

- [11] M. Grosser, U. Schmid, The impact of sputter conditions on the microstructure and on the resistivity of tantalum thin films, Thin Solid Films 517 (2009) 4493.

- [12] A. Mozalev, M. Sakairi, H. Takahashi, H. Habazaki, J. Hubalek, Nanostructured anodic-alumina-based dielectrics for high-frequency integral capacitors, Thin Solid Films 550 (2014) 486

**Jaromír Hubálek** is currently Associate Professor of Faculty of Electrical Engineering and Communication at the Brno University of Technology and head of Laboratory of Microsensors and Nanotechnology. He received his Ph.D. in Microelectronics and Technologies at the Brno University of Technology in 2003. His research activities are primarily focused on micro- and nanotechnologies for sensing. Since 2011 he is also group leader of Smart Nanodevices at CEITEC. He is author or co-author of more than 155 original scientific ISI-indexed peer-reviewed articles in journals and 105 conferences articles with a total of 3081 citations according to Web of Science and he holds 5 patents.

**Michael Schneider**, Ph.D.: is an expert in MEMS/NEMS-related technologies and devices with a strong background in the characterization and application of piezoelectric materials. He has published more than 30 papers with 57 citations.

**Radim Hrdý** is postdoctoral researcher at the Department of Microelectronic, Brno University of Technology. He obtained his PhD degree in 2013. His research interest includes the development of nanostructured surfaces, MEMS structures, sensors for health monitoring and point of care applications. He has authored or co-authored more than 34 papers in peer-reviewed journals and conferences.

**Jan Prášek** received the Ph.D. degree in microelectronics at the Brno University of Technology, Brno, Czech Republic, in 2007, where he is currently a professor assistant at the Department of Microelectronics. His research interests include electrochemical sensors and gas sensors employing nanostructured surfaces developed using nanofabrication techniques. He has authored or co-authored of more than 60 ISI-indexed peer-reviewed articles or book chapters.

**Ulrich Schmid** started studying physics and mathematics at the University of Kassel in 1992. He performed his diploma work at the research laboratories of the Daimler-Benz AG on the electrical characterization of silicon carbide (6H-SiC) microelectronic devices. In 1999, he joined the research laboratories of DaimlerChrysler AG (now Airbus Group) in Ottobrunn/Munich, Germany. In 2003 he received his Ph.D. degree from the Technische Universität München. From 2003 to 2008, he was post-doc at the Chair of Micromechanics, Microfluidics/Microactuators at Saarland University. Since October 2008, he is full professor for Microsystems Technology at the Vienna University of Technology, serving as Director of the Institute of Sensor and Actuator Systems since 2012. He has authored or co-authored more than 300 papers in peer-reviewed journals and conferences and holds as inventor or co-inventor more than 35 granted patent families.