Source: Electronics Weekly article

Adding analogue processing to digital hardware is the key to adaptability and maximum battery life in the nano-scale age, according to the University of Southampton, which is advocating memristors and charge-based processing as the way to do it.

Memristors are non-volatile electrically-adjustable resistors. Made from metal oxides, they scale well and are proposed as memory elements in nanometre-scale logic.

“Over the last five decades we have processed digital signals and have computed using digital techniques, which has taken us very far,” said Southampton researcher Dr Alexantrou Serb. “However, if we are to truly compute at the limits of energy efficiency, that the laws of physics allow, it would seem imperative that we need to move towards analogue computation techniques whilst being much savvier about how to mix analogue and digital signals for maximum effect.”

Earlier this year, the University demonstrated 128 distinct analogue levels stored on a single memristor – equivalent to seven data bits.

“Memristors have gathered a lot of interest as a next generation memory technology by being smaller, more power efficient and yet being able to support more memory states when compared to existing technologies used in our smartphones and computers,” said head of the Electronic Materials and Devices Research Group at Southampton’s Zepler Institute Professor Themis Prodromakis (pictured). “Our group has worked tirelessly in that direction. We soon, however, realised that there is much more to be earned by employing this technology beyond its obvious memory applications.”

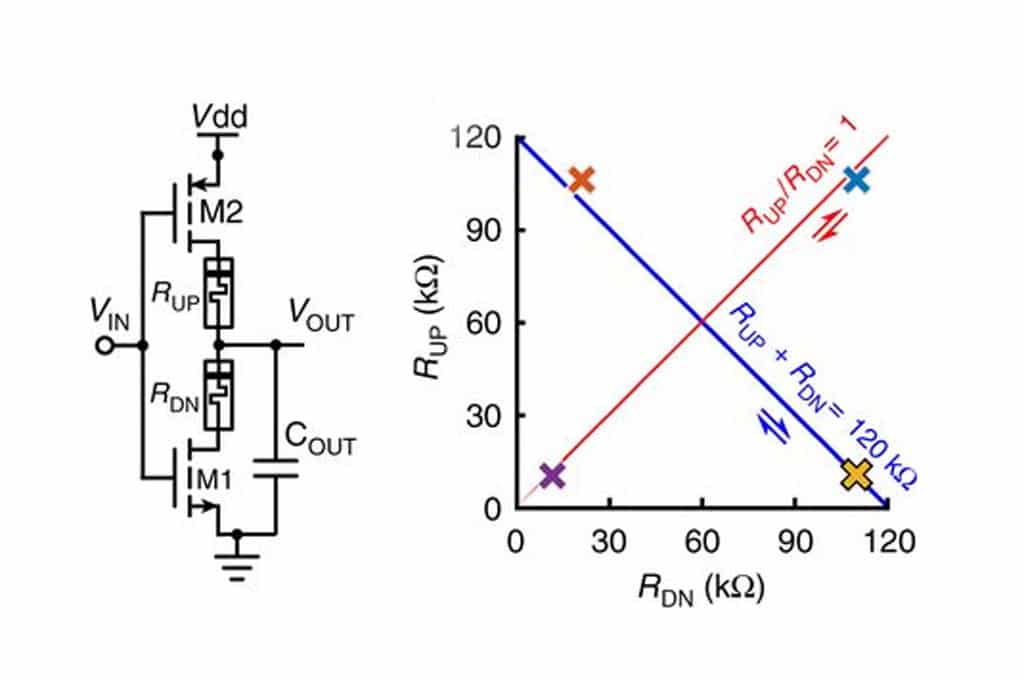

The team has added two memristors into the output totem-pole of a classic CMOS converter, between the usual p-mosfet and n-mosfet – effectively adding a potentiometer, whose wiper is the inverter output.

If both memristors are programmed to be low-resistance, the inverter remains essentially a digital inverter, but if the two memristors are given resistive values, then the output will be a voltage proportional to the ratio of the resistors when both the p and n-mosfets are on, as they are if the input of the inverter is held half-way between 0V and Vdd.

A paper in Nature Communications, ‘Seamlessly fused digital-analogue reconfigurable computing using memristors‘, which describes the work and includes a memristor NAND gate – and is available in full free.

In practice, the output voltage can only be set over a limited range, which the researcher deem suitable for certain artificial intelligence processes.

“A direct impact of this research on modern technologies could be the creation of ultra-efficient AI hardware,” said the University. “AI by nature lends itself to analogue implementation of computation much more readily than to the current digital-based techniques.”

featured image source and credit: Nature Communications and University of Southampton. Reconfigurability modalities in an analogue inverter gate. Memristor-enhanced analogue inverter topology (left picture). Changing the resistive states of the memristors RUP, RDN in the inverter so as to keep their sum (along blue line) or ratio (along red line) constant offers flexibility in controlling the inverter’s transfer characteristics. The constant sum modality allows independent control of transfer characteristic’s plateau height while the constant ratio modality allows for independent control of the plateau’s width (see details in full article).