source: EETimes article

Julien Happich, 6/7/2016

PARIS—Founded in 2005 after having secured a number of patents leveraging the growth of carbon nanofibers (CNFs) on different substrates, Swedish startup Smoltek believes CNFs will play an essential role in shrinking IC packaging.

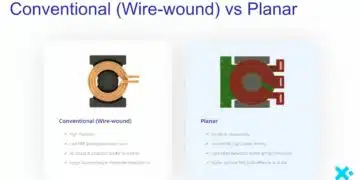

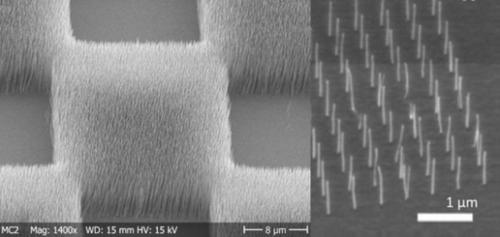

Smoltek’s core technology platform, SmolGROW is what the company claims to be the only process that enables controlled growth of conductive nanostructures at 390°C using CMOS compliant materials and processes. With this low-temperature CNF growth well under control, the company has secured an IP portfolio covering a number of applications including dense 2.5/3D stacking (SmolINPO), ultra-fine pitch interconnects (SmolINCO), integrated capacitors for energy storage or decoupling (SmolCACH), but also thermal interface materials (SmolTIM) for high performance RF and power electronics components and SmolNIL, making use of the CNFs to fabricate high aspect ratio structures through nano imprint lithography (the CNFs have a typical diameter of 50 to 100nm, being from 2 to 150 micrometres long, depending on process parameters).

Contemplating an IP licensing business model, Smoltek’s Chief Innovation Officer & Founder Dr. M. Shafiq Kabir shared his insights with EETimes Europe.

“We will licence our IP to both OSATs and foundries so they can offer the process to their customers on top of silicon, either to integrate new discrete components like our SmolCACH, or to integrate the CNFs in new packaging strategies” Kabir said in an interview.

“We are also working on a Process Design Kit (PDK) for the vertical integration of our process into the IC design flow, because everyone has to be aligned to optimize IC and package integration”.

“You could find our IP in commercial applications within the next two to three years” he said.“With this technology, we are not aiming at replacing Through Silicon Vias (TSVs) yet, but we’ll solve the TSVs/interposer bottleneck. Copper micro-bumps don’t scale too well”, Kabir explained, “copper electro-migration impacts the lifetime reliability of silicon dies, and only CNF-based bumps will be able to scale down with future nodes”.

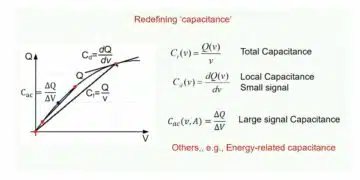

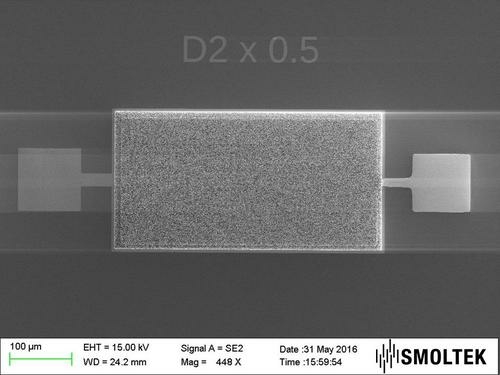

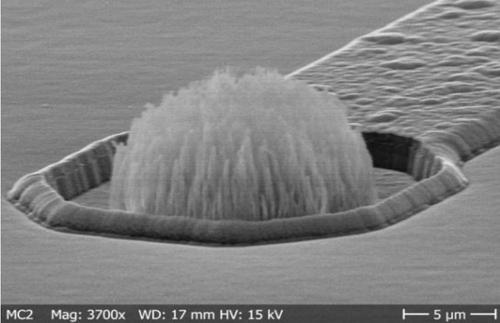

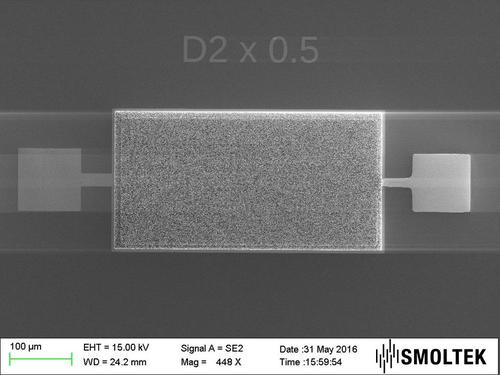

“For the moment we have achieved capacitors with moderate values in terms of capacitance per unit area for the solid state version. However the electrochemical devices show very promising results. The actual values are to be published and we’ll have to wait for some final reviews by our tech team” commented Kabir, accepting to share with us a SEM photograph of a newly manufactured ‘all solid state’ test mini supercapacitor. The SEM photograph shows a carpet of vertically grown CNFs sandwiched between two electrodes.

“The process involves a number of lithography and materials depositions, so you may be seeing some shadows of those different layers”, commented Kabir about the faint square patterns within the rectangular shape.“This particular device has just came out of the lab and has yet to be measured and analysed. However, we have seen an increase of a factor of 5 to 10 of the capacitance per unit area (footprint) compared to the planar counterparts in our first non-optimized version. This new batch is coming out of the lab after some optimization and we will see what it will give us” the CIO said when pressed for some characteristics.

“We are always striving to get the best values out through different technical optimizations. Some target values for performances benchmarking include over 500nF/mm2 in DC with a breakdown voltage to be superior to 2V, and over 1nF/mm2 with a breakdown voltage over 25V for RF applications”.

The vertically aligned CNFs were integrated directly on CMOS using a low-temperature direct current plasma enhanced chemical vapour deposition (DC-PECVD) technique. The paper explained that because the CNFs were made of cone shaped graphene layers stacked on top of each other, the nanostructures obtained had this benefit over carbon nanotubes that they consisted in a completely filled 100% metallic cylinder. Hence they achieved better conducting properties than CNTs whose typical metallic/semiconducting ratio is 1/3 when grown in bulk.

—Julien Happich is editor in chief of for EE Times Europe.

Article originally appeared on EE Times Europe.