This technical blog article written by Oliver Zimmermann and John McCarry, KYOCERA-AVX Components Corporation, explains the functional properties of MLCC ceramic capacitors as an alternative overvoltage and ESD protection.

Introduction – Traditional Electrostatic Protection

Any conductive interface between an electrical circuit and the outside world introduces the possibility of damage through electrostatic discharge (ESD).

Accumulated static charge on a person, a cable, or any similar surface can readily dissipate its stored potential energy upon contact into sensitive components resulting in highly destructive currents.

These voltages can reach the kilovolts and require the addition of specialized circuits and semiconductor devices to protect downstream circuits and ensure continued reliable operation.

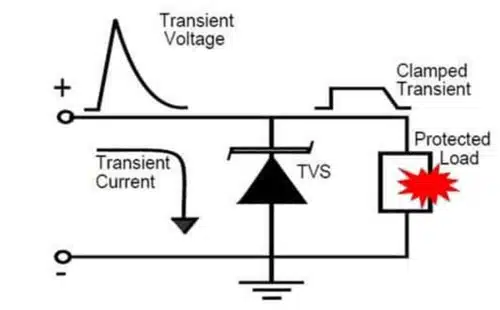

Traditional protection devices include a myriad of different varistors and transient voltage suppression (TVS) diodes. Both operate on the principle of shunting current to ground when the applied voltage exceeds a clamping threshold as shown in figure 1.

Ideally, varistors and TVS diodes only activate to protect the circuit when a high voltage is present and impart no parasitic effects during normal operation.

For high-speed data lines, in particular, it is critical that the protection device introduce as little capacitance as possible (Electronic Design). TVS diodes and varistors are therefore specified not only by their voltage ratings, but also by their capacitance, leakage current, and package options.

This article explains the functional properties of ceramic capacitors as alternative overvoltage protection, the key design considerations of multilayer ceramic capacitors, and finishes with a case study to illustrate these principles.

MLCC Ceramic Capacitors as an ESD Protection Alternative

In practice, many input/output (I/O) lines are not high-speed and can tolerate a fair amount of parasitic capacitance. In these scenarios, a specialized device can be used to gain a significant cost advantage over traditional TVS diodes and varistors: the ESD-safe multi-layer ceramic capacitor (MLCC).

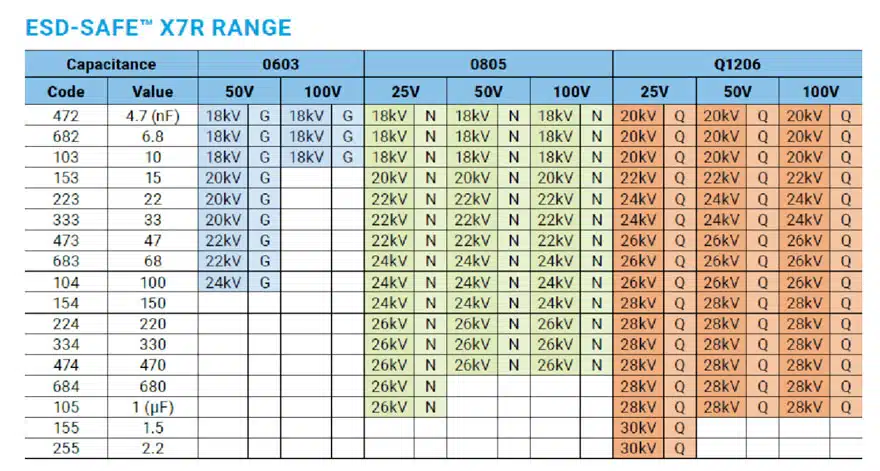

These capacitors contain specialized structures that allow them to tolerate voltage impulses orders of magnitude higher than their continuous DC rating. Examples of X7R devices are shown in table 1. As can be seen, a common 25 V 0805 chip capacitor in this series can withstand 26 kV of ESD.

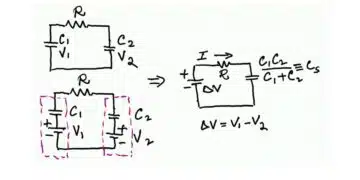

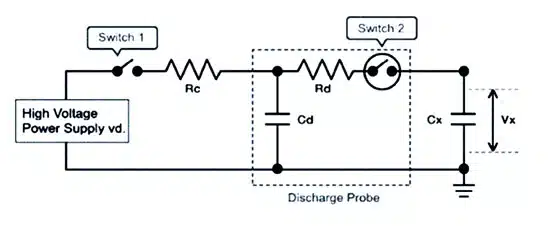

To understand the protection principle behind using these capacitors, consider the typical ESD test circuit shown in figure 2 for the human body model. Rc, Cd, and Rd are specified by the test standard. Cx is the ESD Safe capacitor added across the device to be protected.

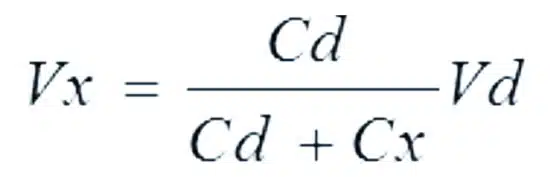

Since Cx is able to safely withstand extremely high ESD voltages, the final voltage (Vx) that will be seen by the downstream circuit will simply be the result of capacitive charge sharing between Cd and Cx. As shown in equation 1, the final output voltage Vx will be significantly reduced by the addition of Cx. If Cx is much larger than Cd, the voltage reduction is substantial.

This simple mechanism provides adequate ESD protection for many I/O lines that are insensitive to the added capacitance. In addition, both cost and space savings are often realized.

Design Considerations for MLCC Protection

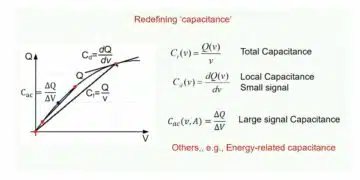

Unlike varistors or TVS diodes, there is no clamping voltage or maximum peak voltage defined for the ESD-safe MLCC. Although the use of ESD-safe protection capacitors can be an effective practice, engineers often overestimate the capacitor’s performance by ignoring its inherent degradation with applied voltage. Generally speaking, the amount of capacitance drop for NPO dielectrics is negligible.

However, the amount of capacitance drop for X7R capacitors can be in the 50% range or even greater. Furthermore, the capacitance drop varies from manufacturer to manufacturer and depends on the material composition used for the X7R dielectric. This drop-in capacitance from the expected value of an X7R capacitor can result in a much higher voltage seen by the IC or device to be protected.

As an example, let us consider a 1nF MLCC used in a circuit with the requirement of 8kV contact discharge based on an ESD model capacitor of 150pF. Using an MLCC with NPO dielectric would result in a theoretically calculated voltage of approximately 1044 volts. On the other hand, using a 1nF capacitor with X7R dielectric which has a 50% drop in capacitance the voltage Vx across the capacitor will approach 1846 volts.

One might simply hope to use NP0 capacitors for all their MLCC protection needs. Unfortunately, NP0 MLCCs are limited in their available maximum capacitance value due to the low dielectric constants. For this reason, in many cases, MLCCs with X7R dielectric must be used to provide sufficient ESD protection.

ESD robustness of MLCC

When used for protection against ESD, the MLCC acts as a capacitive voltage divider. The charge of the ESD pulse is distributed among the capacitive layers, and as the number of active electrodes increases, the robustness of the device follows. In addition, increased thickness of each layer helps to improve the voltage that can be withstood.

As such, the generalized rule is that to maximize MLCC robustness for ESD protection, the designer should incorporate the largest possible capacitance in the largest possible case size to achieve the greatest number of total dielectric layers with maximal thickness.

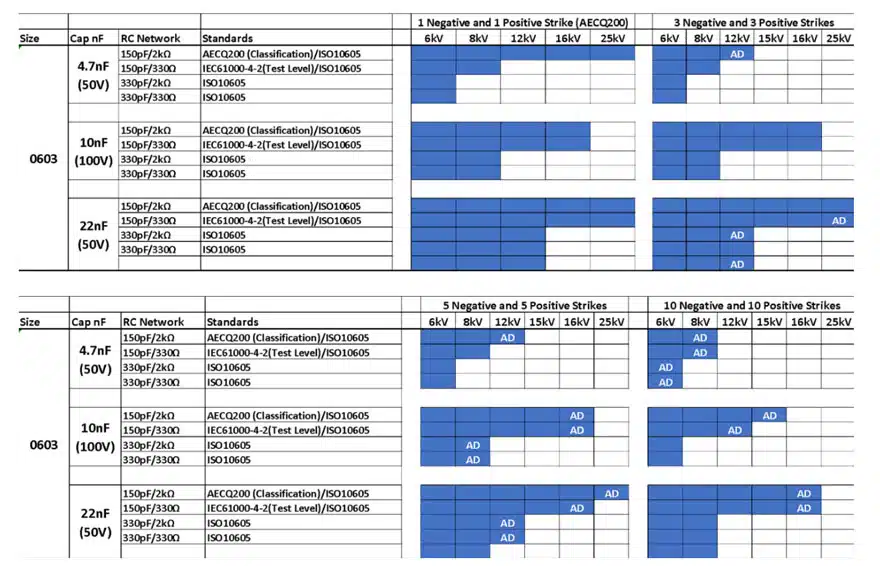

To demonstrate this, KYOCERA AVX carried out ESD robustness tests on a variety of capacitors using the AECQ 200, IEC61000-4-2, and ISO10605 standards. For each run, ten samples of the part were tested. If any single part failed, then the ESD voltage was lowered and ten new parts were tested. Table 2 summarizes these tests for several different 0603 MLCCs, and it is clear that the most robust part is the 22nF device.

Case Study

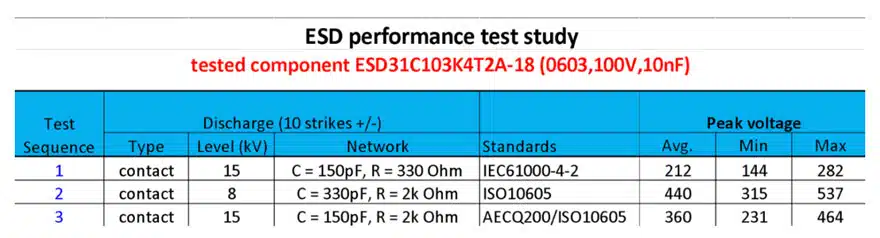

The following test setup describes an example ESD test performed on a 0603 ESD-safe MLCC. Not only has the ESD withstand level been measured, but also the maximum peak voltage across the capacitor. An additional load resistor of 33 kOhm has been used in this test setup representing the input impedance of the downstream circuit.

The following equipment and measurements were used for the test:

- PCB-board: FR4 PCB test board 2 layer, 1.5mm

- Load resistor: 33kΩ ±1%

- High voltage probe: P6015A (Tektronix)

- Oscilloscope (digital): MSO54-5-BW-2000 (Tektronix)

- 10 strikes (+/-) per unit.

The predetermined pass criteria for the test is:

- Tested components are within the electrical limits and with no mechanical defects after the tests.

As can be seen in the results in table 3, the MLCC capacitor safely reduces the applied ESD discharge by orders of magnitude. As long as the downstream components are rated to tolerate this reduced voltage, adequate protection can be realized in a simple, small, and cost-effective manner.

Conclusion

MLCC ceramic capacitors offer an inexpensive alternative to protecting I/O lines where speed is not critical. The KYOCERA AVX ESD-Safe™ Series provides a wide range of ESD robust MLCC’s tested according to the AECQ200, IEC61000-4-2, and ISO10605 standards.

In applications where MLCC’s cannot be used, it is recommended to simply use the more traditional Multilayer Varistor (MLV).