Würth Elektronik has published a new Application Note: “ANP121 – Filter and surge protection for I2C-Bus” that explains interference suppression methods and common techniques.

In this new note, the supplier of electronic and electromechanical components provides valuable support to developers who use the I²C bus (Inter-Integrated Circuit Bus) in cross-circuit-board scenarios.

An extension of the interface via connectors or cables can, however, potentially make the I²C bus susceptible to external interference such as electrostatic discharge (ESD), burst, and radiated RF.

The purpose of this Application Note is to present a suitable filter and protection circuit that increases the noise immunity of the I²C bus without compromising the signal quality of the data and clock lines.

The latest addition to the collection of application-specific tips on Würth Elektronik’s support sites comprises the sections “Overview I2C bus“, “Overview I2C specifications”, ”Selection of the filter and overvoltage protection components”, “LTspice simulation with 400 kHz clock rate“, and „”Measurement of a real application with 400 kHz clock rate“. The Application Note was created by building simulation models in LTspice and measuring them in a real-life application to verify the results of the simulation.

Test set-up with FeatherWing

To verify the simulation, additional measurements were made on a Würth Elektronik SensorBLE FeatherWing kit. This kit consists of a master board with a microcontroller and two other boards equipped with a WE Bluetooth module and a FeatherWing system with WE sensors (3-axis acceleration, temperature, humidity, pressure).

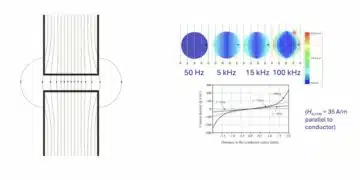

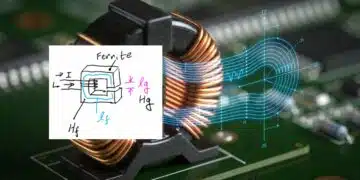

The master board communicates with the other two boards via I²C bus at a maximum data rate of 400 kBit/s. A data cable 20 cm (7.87 inch) long was used to connect the sensor board to the rest of the I²C. A parasitic capacitance of 400 pF with respect to GND was simulated using MLCCs. The simulation and measurement showed that SMT multilayer ferrites in combination with ESD protection diodes have practically no effect on the data signal (SDA) and the clock signal (SCL) of the I²C bus, but rather enhance the noise immunity of the I²C bus.