Murata has released a new technical guide on power delivery networks (PDNs) for AI servers in next‑generation data centers, focusing on improving power stability and reducing distribution losses.

The document is particularly relevant for design engineers and component purchasers specifying capacitors, inductors and EMC components into high‑density power systems where AI compute loads are pushing existing infrastructure to its limits.

Why PDN design matters for AI data centers

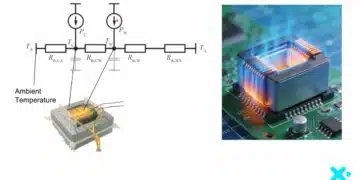

AI servers operate with rapidly changing load currents, high peak power, and increasing bus voltages, all within extremely dense rack configurations. This combination makes the power delivery network a critical part of system performance, reliability, and total cost of ownership for data center operators.

At rack and board level, poor PDN design can lead to voltage droop, instability, excessive losses and thermal issues that directly affect server uptime and AI accelerator performance. The Murata guide addresses these issues from a system perspective, linking market trends in AI data centers to concrete implementation strategies in power circuit design.

Key focus areas of the Murata guide

The technology guide “Optimizing Power Delivery Networks for AI Servers in Next‑Generation Data Centers” is structured to support engineers through both conceptual and practical aspects of PDN development.

Key topics covered include:

- Market overview of power consumption trends in AI data centers and how rising compute density and higher voltage operation impact PDN design.

- Breakdown of power delivery topologies and power placement architectures across racks, power shelves, boards and point‑of‑load stages.

- Typical challenges in high‑current AI server power rails, including stability, transient response, distribution loss and thermal management.

- Design‑oriented guidance on component selection and placement for optimal PDN impedance and loss reduction.

- Examples of how evolving PDN architectures can improve both power stability and efficiency at system level.

For component engineers, the value of the guide lies in connecting abstract PDN concepts—such as impedance vs. frequency, decoupling hierarchy and placement trade‑offs—with concrete component classes and technologies.

Murata component portfolio for AI server PDNs

Murata underpins the PDN methodology presented in the guide with a broad passive component lineup tailored to modern data center requirements.

The portfolio relevant to AI server power delivery includes:

- Multilayer ceramic capacitors (MLCC)

- Silicon capacitors

- Polymer aluminum electrolytic capacitors

- Inductors

- Chip ferrite beads

- Thermistors

Each of these component types addresses a different part of the PDN problem:

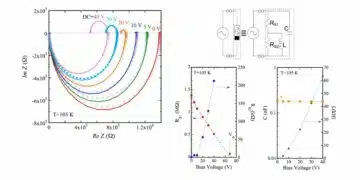

- MLCC and silicon capacitors: Low‑ESR, low‑ESL decoupling close to high‑speed processors and ASICs, supporting fast current transients and noise suppression at high frequencies.

- Polymer aluminum electrolytic capacitors: Bulk energy storage and smoothing at intermediate nodes, where high ripple currents and long‑term reliability are key.

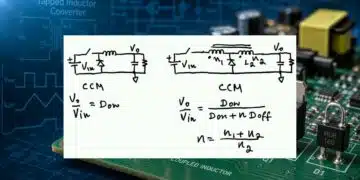

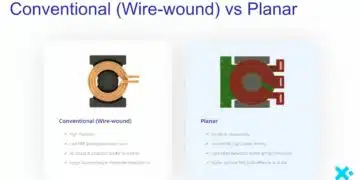

- Inductors: Core elements of DC‑DC converters and point‑of‑load regulators, where low loss, saturation characteristics and thermal performance are critical.

- Chip ferrite beads: EMI suppression on power lines and sensitive signal paths, helping to meet EMC requirements while containing noise within the rack.

- Thermistors: Temperature sensing and inrush control, important for protection, system monitoring and safe startup of high‑power stages.

The guide positions these components within practical PDN architectures, emphasizing that performance is determined not only by individual part selection but also by how components are combined and placed in the power tree.

Design‑in notes for engineers

From a design‑in perspective, several practical considerations emerge that are directly relevant for engineers specifying Murata components into AI server platforms:

- Treat the PDN as a multi‑level system: Use a hierarchy of bulk, intermediate and high‑frequency decoupling rather than relying on a single capacitor technology to cover the entire frequency range.

- Pay attention to placement: The effectiveness of MLCCs and silicon capacitors is highly dependent on loop inductance; minimizing distance and optimizing layout can be as important as the nominal capacitance value.

- Consider voltage trends: As data centers move toward higher bus voltages to reduce distribution losses, verify component voltage ratings and derating strategies according to the manufacturer datasheet rather than relying on legacy design rules.

- Balance efficiency and stability: Inductor selections and converter architectures should be evaluated both for conversion efficiency and for their impact on PDN stability and transient behavior at the AI accelerator rails.

- Design with EMC in mind from the outset: Integrate chip ferrite beads and other EMI suppression components into the PDN early in the design cycle, taking into account likely regulatory and customer EMC requirements.

- Use thermal and reliability analysis: High power densities in AI racks make thermal performance and lifetime of capacitors and inductors critical; lifetime estimates and allowable hot‑spot temperatures should be checked against the respective datasheets.

Murata also highlights the use of advanced analysis tools to support component selection and placement, which is particularly useful in complex AI boards where traditional rule‑of‑thumb decoupling approaches are no longer sufficient.

Relevance for purchasing and supply chain

For purchasing and supply‑chain professionals, the guide and accompanying Murata portfolio highlight several points:

- Broad technology coverage from a single supplier (MLCC, silicon, polymer aluminum, inductors, ferrites, thermistors) simplifies qualification and supply management.

- A strong global supply and support network is important for large data center programs, where synchronized ramp‑up across multiple regions is often required.

- Close collaboration between design teams and suppliers on PDN optimization can reduce over‑design (for example, excessive capacitor counts) and help control BOM cost without sacrificing stability.

Given the rapid rollout of AI‑focused data centers, aligning PDN component strategies with suppliers that can support design‑stage analysis and long‑term availability is becoming a strategic consideration rather than a purely tactical sourcing decision.

Typical application areas in the PDN

Within an AI server or rack, the Murata components referenced in the guide are typically used in:

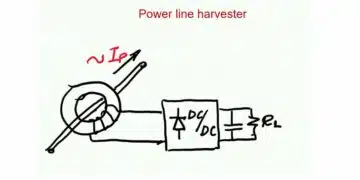

- Rack‑level power distribution units and bus converters

- Power shelves and intermediate bus converters supplying server boards

- Board‑level DC‑DC converters and point‑of‑load regulators for CPUs, GPUs and AI accelerators

- High‑current core, memory and I/O rails on server and accelerator boards

- Management, control and networking subsystems requiring clean and stable auxiliary rails

In all of these areas, the combination of appropriate capacitor technologies, inductors and EMI components is central to achieving both electrical performance and compliance with data center‑level efficiency targets.

Accessing the Murata technology guide

The technology guide “Optimizing Power Delivery Networks for AI Servers in Next‑Generation Data Centers” is available as a downloadable resource. Engineers can obtain the full document, including diagrams and detailed examples, directly from the Murata website.

In addition, Murata offers broader information on its data center initiatives and product lines via its campaigns, articles and general product pages, which can be useful when aligning PDN design work with component roadmaps and long‑term availability.

Source

This article is based on an official Murata Manufacturing Co., Ltd. press release and associated information published on the Murata website, reformatted and expanded with additional neutral technical context for design and component engineering audiences.